Ce consortium est présidé par le fondateur du Web : Sir Tim Berners-Lee (et lauréat du prix Turing).

Dernière chose, last but not least, le W3C met à disposition un validateur de code HTML, ici :

Un 1er paragraphe. On remarque qu'un saut de ligne dans le code source, ne correspond pas à un saut de ligne dans le navigateur.

En UTF-8, pas de souci pour ces caractères spéciaux : € ≤ ≥ ≠ ...

Cependant quelques caractères spéciaux doivent être écrits en

entités HTML

Voici ci-dessous une liste (ul : unordered list) où chaque élément

est appelé un list item (li) :

Dans un bon navigateur, on peut visualiser le code source de toute page HTML en faisant :

Le World Wide Web Consortium "W3C" est un organisme régissant

les règles du web.

Ce consortium est présidé par le fondateur du Web : Sir

Tim Berners-Lee (et lauréat du prix Turing).

Dernière chose, last but not least, le W3C met à disposition un validateur de code HTML, ici :

![]()

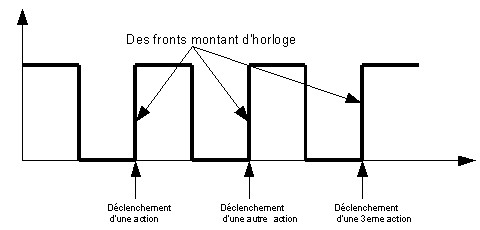

En microarchitecture, un pipeline (ou chaîne de traitement), consiste à découper une instruction en plusieurs étapes.

Avec un pipeline, le processeur peut commencer une nouvelle instruction sans avoir terminé la précédente.

==> Donc un gain de temps !

Considérons ces 5 étapes nécessaires pour traiter une instruction :

| code | dénomination | description |

|---|---|---|

| IF | Instruction Fetch Fetch = Va chercher |

Charge l'instruction à exécuter dans le pipeline |

| ID | Instruction Decode | Décode l'instruction et adresse les registres |

| EX | Execute | Exécute l'instruction (par l'unité arithmétique et logique : ALU) |

| MEM | Memory |

Accède à la mémoire : * soit en lecture : dans le cas d'une instruction du type STORE * soit en écriture : dans le cas d'un LOAD |

| WB | Write Back |

Ecrit le résultat dans un registre. Une écriture en registre WB fait suite à : * un LOAD (RAM → registre) * un MOV (registre → registre) * ou un calcul de l'ALU |

En supposant que chaque étape met 1 cycle d'horloge pour s'exécuter.

==> Il faut normalement 5 cycles pour exécuter une instruction !

==> Il faut 15 cycles pour réaliser 3 instructions !!!

Le 1er ordinateur à utiliser cette technique est l'IBM Stretch,*

conçu en 1961.

C'est une forme de multitâche .. comparable à une ligne de montage en industrie.

Chacune des étapes d’un pipeline est appelé étage.

Le nombre d'étages d'un pipeline est appelé sa profondeur.

Pour un processeur doté d'un pipeline à 5 étages, il faut 9 cycles pour

exécuter 5 instructions.

À t = 5, tous les étages du pipeline sont sollicités, et les 5 opérations

ont lieu en même temps.

Aujourd'hui les processeurs ont des profondeurs supérieures à 10.

Oups ... l'image ligne 135 ne s'affiche pas dans le navigateur.

Et oups bis ! ... le Validator

m'indique 2 erreurs, aidez-moi à corriger ces 3 problèmes :

p element in scope but a p end tag seen.img element must have an alt attribute,

except under certain conditions. For details, consult guidance

on providing text alternatives for images.